International Journal of ELECTROCHEMICAL SCIENCE www.electrochemsci.org

Short Communication

# **Effects of Doped Stannum in the Fabrication of Zinc-Oxide Thin-Film Transistors**

Hsin-Chiang You<sup>1,\*</sup>, Cheng-Yen Wu<sup>2</sup>, Wen-Luh Yang<sup>3</sup>

<sup>1</sup>Department of Electronic Engineering, National Chin-Yi University of Technology, Taichung, Taiwan

<sup>2</sup>Ph.D. Program of Electrical and Communications Engineering, Feng Chia University, Taichung, Taiwan

<sup>3</sup>Department of Electronic Engineering, Feng Chia University, Taichung, Taiwan

\*E-mail: <u>hcyou@ncut.edu.tw</u>

Received: 23 April 2015 / Accepted: 14 March 2016 / Published: 1 April 2016

A sol-gel method was applied with acetates as precursors under standard atmospheric conditions to fabricate ZnO semiconducting thin-films. We evaluated the performances of thin-film transistor (TFT) which has a ZnO active channel layer and the effects of stannum (Sn) doping on the threshold voltage of ZnO TFTs at a low temperature (300 °C), which was compared with the performances of the undoped ZnO and stannum-doped zinc oxide (ZTO) TFT. The electrical characteristics of thin-films and TFTs doped with stannum concentrations of 0.3 mole ratio were examined; and reductions at the threshold voltage of 5.6 V were found. At 300 °C, it was observed that the stannum-doped zinc oxide (ZTO) device has a mobility of  $4.2 \times 10^{-4}$  cm<sup>2</sup>/V-s, a threshold voltage of 5.3 V, and an on/off current ratio of  $10^4$ .

Keywords: Thin-film transistor, threshold voltage, zinc tin oxide, ZnO, ZTO

## **1. INTRODUCTION**

Generally, electrodes in displays [1] have used metal oxide thin-films, such as In<sub>2</sub>O<sub>3</sub>, SnO<sub>2</sub>, and ZnO. Recently, in drive transistors [2, 3], an active channel layer has been intensively studied for application. These continuous processes typically involve high vacuum deposition, such as chemical vapor deposition (CVD) and physical vapor deposition (PVD), which contribute to high costs. The solution processes used for ZnO film deposition in atmospheric environments include the sol-gel method and chemical bath deposition (CBD) [4, 5]. By using a sol-gel method, ZnO TFTs fabricated can be achieved using halide and organic precursors in numerous solvents [6-10]. Chlorides are used doi: 10.20964/10089

as precursors for sol-gel ZnO materials; however, chloride is toxic. In this study, the sol-gel processed ZnO TFT was derived from acetate salts [11]. Numerous studies have demonstrated transparent ZnO TFTs doped with combinations of Ga, In, and Sn, such as indium zinc oxide (IZO) [11], indium gallium zinc oxide (GIZO) [12], and zinc tin oxide (ZTO) [13]; however the cost of indium is high. The ionic radius of Sn<sup>4+</sup> is 0.69 Å and smaller compared with the ionic radius (0.74 Å) of Zn<sup>2+</sup>; thus, Sn<sup>4+</sup> ions can replace Zn<sup>2+</sup> ions in substitutional sites [14]. However, few studies have examined Sn doped ZnO TFTs made by using a sol-gel process [15, 16].

This ZnO semiconductor thin-films made using a sol-gel method are examined at various annealing temperatures under standard atmospheric conditions, and acetates are used as precursors [17-24]. The performance of TFTs with a ZnO active channel layer and the compatibility of Sn doped ZnO (ZTO) TFT for various doping levels with a low temperature process (300  $^{\circ}$ C) were evaluated [25-31].

### 2. EXPERIMENTAL DETAILS

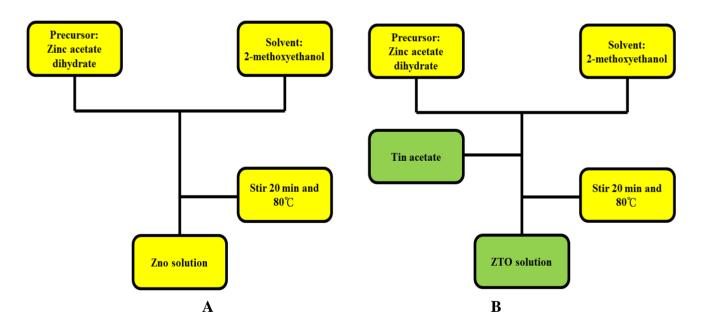

The ZnO and ZTO precursor solutions synthesized uses zinc acetate dihydrate and tin (IV) acetate. The solutions (0.05M in metal precursors) were made in 2-methoxyethanol (2ME). The Sn/Zn molar ratio of ZTO precursor solutions was 0.3 mole ratio. The metal oxide solutions were stirred at 80 °C for 30 min before applying spin-coating, as shown in the solution flow chart in Fig. 1 [15, 31].

Figure 1. The preparation of the (a) ZnO, (b) ZTO solution use the sol-gel method

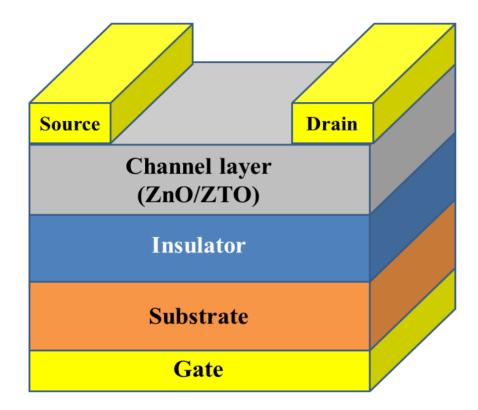

RCA clean was used to treat all prepared p-type silicon wafers, and then a  $SiO_2$  film with a thickness of approximately 100 nm was grown by thermal oxidation. After  $SiO_2$  formation, oxygen plasma was used to treat the surface for 30 s. ZnO or ZTO films deposited was made by spin coating at

1000 rpm for 30 s under an ambient temperature of 25 °C. ZnO or ZTO solution was spin to obtain the film that was then annealed for 1 hour at 300 °C in air. Finally, a thermal evaporation (pressure  $10^{-6}$  Torr) process was used to back plate the wafer with Al, and 300 nm Al was defined as the gate electrode followed by a shadow mask to define the source and drain, which were both plated with Al = 300 nm. Fig. 2 shows a schematic cross-sectional view of the ZnO and ZTO structure. The devices were measured using an Agilent 4156.

Figure 2. A schematic cross-sectional view of the ZnO and ZTO Thin-Film Transistors structure.

#### **3. RESULTS AND DISCUSSION**

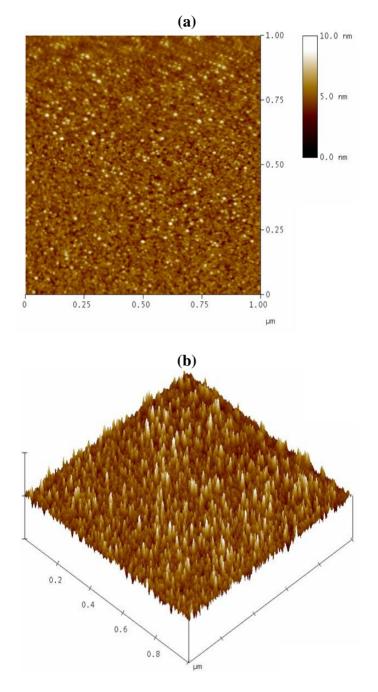

The surface morphology of the thin-film is crucial in a transistor. Images were acquired in contact mode, and the collected scan area was 1  $\mu$ m×1  $\mu$ m. Fig. 3 shows the AFM images of the solgel-derived ZnO thin films. After exposure for 1 hour at 300 °C in air, the sample had a root mean square (RMS) roughness of 0.635 nm. A smooth thin-film surface was obtained using the sol-gel method.

**Figure 3.** AFM images of the ZnO thin films annealed at 300°C, the scanning area of 1  $\mu$  m<sup>2</sup> (a) RMS roughness analysis 0.635 nm and (b) Three-dimensional AFM image.

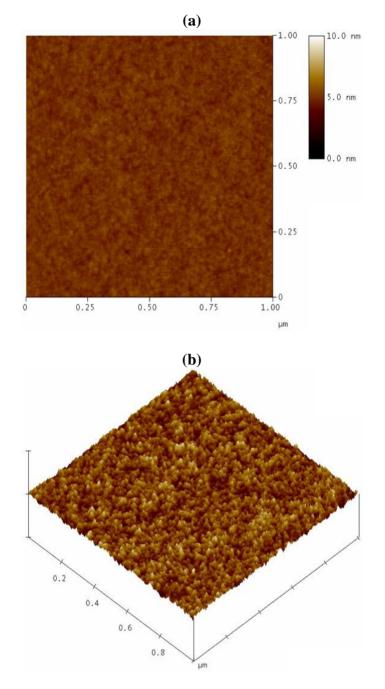

The AFM image of the Sn-doped ZnO thin-film is shown in Fig. 4. At Sn concentrations of 0.3 mole ratio, the root mean square (RMS) roughness was 0.375 nm. The surface of the un-doped ZnO was annealed at 300 °C (RMS = 0.635 nm), and was greater compared with Sn concentrations, which is 0.3 mole ratio (RMS = 0.375 nm). The addition of Sn improved the surface smoothness due to decreasing the grain size [14, 32]. These AFM results revealed that the Sn-doped ZnO thin-film showed good quality.

**Figure 4.** AFM images of the ZTO thin films (Sn concentrations of 0.3 mM) annealed at 300°C, the scanning area of 1  $\mu$ m<sup>2</sup> (a) RMS roughness analysis 0.375 nm and (b) Three-dimensional AFM image.

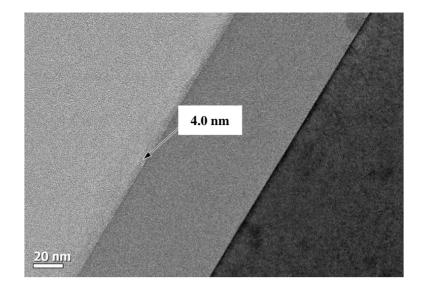

The morphology of the ZnO/SiO<sub>2</sub> structures into an ultrathin film was observed by a fieldemission TEM tool (JEOL JEM-2100F). In Fig. 5 shows cross-sectional TEM images of the ZnO/SiO<sub>2</sub> whose structures were annealed at 300 °C [15]. Smooth and conformal interfaces were observed in the sample. The TEM images show that the structure by the sol-gel method resulted in an approximately 4.0 nm-thick ZnO film, which is a smooth semiconductor layer in the device. The surface morphology of the thin-film is crucial in a transistor.

Figure 5. Cross-sectional TEM images of sol-gel-derived ZnO/SiO<sub>2</sub> structures annealed at 300°C[15].

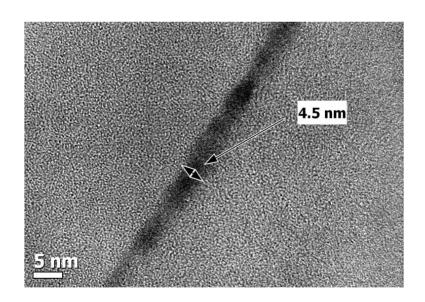

The morphology of the ZTO/SiO<sub>2</sub> structures into an ultrathin film was observed by a fieldemission TEM tool (JEOL JEM-2100F). Fig. 6 shows a cross-sectional TEM image of the ZTO/SiO<sub>2</sub> whose structures were annealed at 300 °C with Sn concentrations of 0.3 mole ratio in ZTO thin-films. The amorphous nature of the approximately 4.5 nm-thick ZTO film was verified using TEM. Smooth and conformal interfaces were observed in the sample. The sol-gel method resulted in a smooth ZTO film.

Figure 6. Cross-sectional TEM images of sol-gel-derived ZTO/SiO<sub>2</sub> structures of Sn concentrations of 0.3 mM and annealed at  $300^{\circ}$ C.

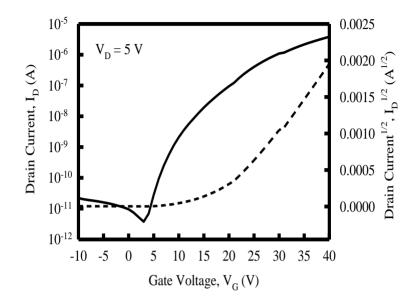

An Agilent 4156C analyzer was used to measure the drain current-gate voltage  $(I_D-V_G)$  transfer characteristic. Fig. 7 shows that at room temperature the drain current-gate voltage  $(I_D-V_G)$  transfer

characteristic curves of ZnO TFT that have a channel length of 70  $\mu$  m and width of 2000  $\mu$  m [15]. The ZnO TFT showed an on-off current ratio (I<sub>on</sub>/<sub>off</sub>) of up to nearly 10<sup>5</sup>. The on-current (I<sub>on</sub>) achieved can sustain as high as  $3.81 \times 10^{-6}$  A for V<sub>D</sub> = 5 V, and the off-current (I<sub>off</sub>) is as low as  $2.18 \times 10^{-11}$  A; the device has a field effect mobility ( $\mu_{FE}$ ) of 0.06 cm<sup>2</sup>/V-s and a threshold voltage (V<sub>th</sub>) of 15.6 V.

Figure 7. Transfer characteristics curves of ZnO TFT annealed at 300  $^{\circ}$ C by sol-gel method, V<sub>D</sub> = 5 V [15].

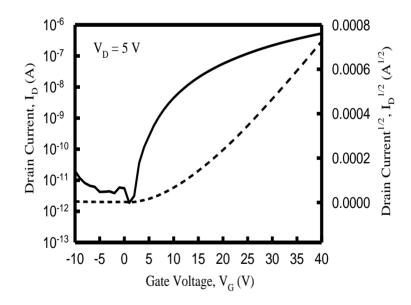

Figure 8. Transfer characteristics curves of ZTO TFT with Sn concentrations of 0.3 mM and annealed at 300 °C by sol-gel method,  $V_D = 5$  V.

The drain current-gate voltage  $(I_D-V_G)$  transfer characteristic was measured using an Agilent 4156C analyzer. Fig. 8 shows the drain current  $(I_D)$  as a function of gate voltage  $(V_G)$  of the ZTO TFT

with Sn concentrations of 0.3 mole ratio. The V<sub>D</sub> was fixed at 5 V, and V<sub>G</sub> varied from -10 to 40 V. The drain current-gate voltage (I<sub>D</sub>-V<sub>G</sub>) transfer characteristics with Sn concentrations of 0.3 mole ratio showed that the on-off current ratio (I<sub>on/off</sub>) was 10<sup>4</sup> and the on current (I<sub>on</sub>) was as high as  $5.26 \times 10^{-7}$  A. The threshold voltage (V<sub>th</sub>) and field effect mobility ( $\mu_{FE}$ ) of the device were 5.6 V and  $0.42 \times 10^{-3}$  cm<sup>2</sup>/V-s, respectively.

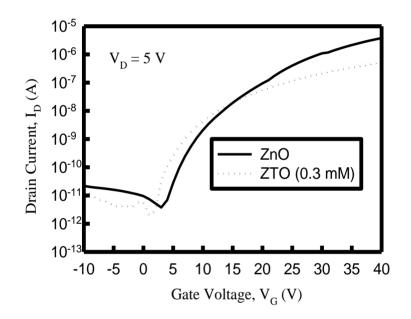

An Agilent 4156C analyzer was used to measure the drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristic. Fig. 9 shows the  $I_D$ - $V_G$  transfer characteristics for TFT based on ZnO (un-doped) and ZTO (0.3 mole ratio). The device performance parameters included the on current ( $I_{on}$ ), off current ( $I_{off}$ ), on-off current ratio ( $I_{on}/_{off}$ ), threshold voltage ( $V_{th}$ ), and field effect mobility ( $\mu_{FE}$ ). The TFTs operated as n-type channels in enhancement mode.

Figure 9. Transfer characteristics of TFT fabricated using ZTO channel annealed at  $300^{\circ}$ C with different Sn concentrations ranging from 0 to 0.3mM,  $V_D = 5 \text{ V}$ .

**Table 1.** Electrical performance parameters of transistors fabricated using a ZTO channel annealed at  $300^{\circ}$ C with Sn/Zn mole ratio.

| mole ratio of<br>Sn : Zn | I <sub>on</sub> (A)   | $I_{off}(A)$           | I <sub>on/off</sub> | $V_{th}(V)$ | $\mu_{FE}$ (cm <sup>2</sup> /V-s) |

|--------------------------|-----------------------|------------------------|---------------------|-------------|-----------------------------------|

| 0/1                      | 3.81×10 <sup>-6</sup> | 2.18×10 <sup>-11</sup> | 10 <sup>5</sup>     | 15.6        | 60×10 <sup>-3</sup> [15]          |

| 0.3/1                    | 5.26×10 <sup>-7</sup> | 4.97×10 <sup>-11</sup> | $10^{4}$            | 5.6         | 0.42×10 <sup>-3</sup>             |

Electrical analysis showed that the field effect mobility ( $\mu_{FE}$ ) of these TFTs ranged between  $0.42 \times 10^{-3}$  and  $60 \times 10^{-3}$  cm<sup>2</sup>/V-s, on-off current ratios ( $I_{on/off}$ ) were  $10^4 - 10^5$ , and threshold voltages ( $V_{th}$ ) were 5.6 - 15.6 V. These were compared with the un-doped ZnO TFT without an Sn component

annealed at 300 °C. By reducing the Sn content, the on-off current ratio ( $I_{on/off}$ ) decreased from approximately  $10^5$  to  $10^4$ , the threshold voltage ( $V_{th}$ ) shifted from 15.6 to 5.6 V, and the field effect mobility ( $\mu_{FE}$ ) reduced from  $60 \times 10^{-3}$  to  $0.42 \times 10^{-3}$  cm<sup>2</sup>/V-s, as shown in Table 1 [15]. The threshold voltage was derived as

$$V_{\rm TN} = \frac{\left| Q_{\rm SD}^{(\rm max)} \right|}{C_{\rm ox}} + V_{\rm FB} + 2\phi_{\rm fn}$$

(1)

where  $Q'_{SD}(max)$ ,  $C_{ox}$ ,  $V_{FB}$ , and  $2\phi_{fn}$  are the maximal space charge density, gate oxide capacitance, flat band voltage, and potential difference between  $E_{Fi}$  and  $E_F$  in n-type, respectively. The carrier concentration was low when the low  $Sn^{+4}$  was low, which reduced the threshold voltage ( $V_{th}$ ), as shown in (1). The low mobility can be attributed to grain boundary scattering caused by a less dense microstructure [32]. For the low  $Sn^{+4}$  content samples, the low mobility and low threshold voltage are the principal causes of the low current ( $I_{on}$ ) and low on-off current ratio ( $I_{on/off}$ ) [15,31,33,34].

#### **4. CONCLUSION**

This paper presents a low cost and simple method to fabricate a ZnO TFT that is suitable for depositing onto an active channel layer of ZnO and ZTO using a sol-gel method. The ZnO TFT fabricated under low temperature (300 °C) had an on-off current ratio ( $I_{on/off}$ ) of 10<sup>5</sup>, field effect mobility ( $\mu_{FE}$ ) of 0.06 cm<sup>2</sup>/V-s, and threshold voltage ( $V_{th}$ ) of 15.6 V. The TFT was fabricated using the sol-gel method by coating the active channel layer of ZTO and annealing at 300 °C; the threshold voltage ( $V_{th}$ ) decreased to 5.6 V at Sn concentrations of 0.3 mole ratio. The ZnO and ZTO TFTs fabricated using the sol-gel method with a standard atmospheric pressure technique may be applied to next generation flexible electronics.

#### **ACKNOWLEDGMENTS**

This work was supported by the Ministry of Science and Technology, Taiwan, under Contract Nos. MOST 104 - 2221 - E - 167 - 012.

### References

- 1. K. Nomura1, H. Ohta1, K. Ueda, T. Kamiya1, M. Hirano1, H. Hosono1, *Science*, 300 (2003) 1269.

- 2. M. Grundmann, H. Frenzel, A. Lajn, M. Lorenz, F. Schein, H. V. Wenckstern, *Physica Status Solidi (a)*, 207 (2010) 1437.

- 3. H. C. Cheng, C. F. Chen, and C. Y. Tsay, Appl. Phys. Lett., 90 (2007) 012113.

- 4. C. Voss, Y. J. Chang, S. Subramanian, S. O. Ryu, T. J. Lee, C. H. Chang, *J. Electrochem. Soc.*, 151 (2004) C655.

- 5. Y. J. Changa, D. H. Leea, G. S. Hermanb, C. H. Changa, *Electrochem. Solid State Lett.*, 10 (2007) H135.

- 6. K. H. Cho, M. G. Kang, S. M. Oh, C. Y. Kang, Y. Lee, S. J. Yoon, *Thin Solid Films*, 518 (2010) 6277.

- 7. H. C. Cheng, P. Y. Yang, J. L. Wang, S. Agarwal, W. C. Tsai, S. J. Wang, I.C. Lee, *IEEE Electron Device Lett.*, 32 (2011) 497.

- 8. T. Hirao, M. Furuta, T. Hiramatsu, T. Matsuda, C. Li, H. Furuta, H. Hokari, M. Yoshida, H. Ishii, M. Kakegawa, *IEEE Trans. Electron Devices*, 55 (2008) 3136.

- 9. M. S. Wu, W. C. Shih, W. H. Tsai, J. Phys. D-Appl. Phys., 31 (1998) 943.

- 10. C. Lee, K. Lim, J. Song, Sol. Energy Mater. Sol. Cells, 43 (1996) 37.

- 11. C. G. Choi, S. J. Seo, B. S. Bae, Electrochem. Solid State Lett., 11 (2008) H7.

- 12. J. H. Noh, C. S. Kim, S. Y. Ryu, S. J. Jo, Jpn. J. Appl. Phys., 46 (2007) 4096.

- 13. H. Q. Chiang, J. F. Wager, R. L. Hoffman, J. Jeong, D. A. Keszler, *Appl. Phys. Lett.*, 86 (2005) 013503.

- 14. C. Y. Tsay, H. C. Cheng, Y. T. Tung, W. H. Tuan, C. K. Lin, Thin Solid Films, 517 (2008) 1032.

- 15. H. C. You, Y. H. Lin, Int. J. Electrochem. Sci., 7 (2012) 9085.

- 16. C. Y. Tsay, K. S. Fan, S. H. Chen, C. H. Tsai, J. Alloy. Compd., 495 (2010) 126.

- 17. J. H. Lee, K. H. Ko, B. O. Park, J. Cryst. Growth, 247 (2003) 119.

- 18. D. Kim, Y. Jeong, K. Song, S. K. Park, G. Cao, J. Moon, Langmuir, 25 (2009) 11149.

- H. Bahadur, A. K. Srivastava, D. Haranath, H. Chander, A. Basu, S. B. Samanta, K. N. Sood, R. Kishore, R. K. Sharma, Rashmi, V. Bhatt, P. Pal, S. Chandra, *Indian J. Pure Appl. Phys.*, 45 (2007) 395.

- 20. S. Muthukumar, C.R. Gorla, N.W. Emanetoglu, S. Liang, Y. Lu, J. Cryst. Growth, 225 (2001) 197.

- 21. R. L. Hoffman, B. J. Norris, J. F. Wager, Appl. Phys. Lett., 82 (2003) 733.

- 22. G. Rendón, P. Poot, A.I. Oliva, F.J. Espinosa-Faller, J. Appl. Res. Technol., 10 (2012) 549.

- 23. E. R. Vázquez-Cerón, V. R. Barrales-Guadarrama, E. M. Rodríguez-Rodríguez, R. Barrales-Guadarrama, J. Appl. Res. Technol., 5 (2007) 113.

- 24. S.J. Lim, S. Kwon, H. Kim, Thin Solid Films, 516 (2008) 1523.

- 25. S. Y. Park, B. J. Kim, K. Kim, M. S. Kang, K. H. Lim, T. I. Lee, J. M. Myoung, H. K. Baik, J. H. Cho, Y. S. Kim, *Adv. Mater.*, 24 (2012) 834.

- 26. M. C. Chu, H. C. You, J. S. Meena, S. H. Shieh, C. Y. Shao, F. C. Chang, F. H. Ko, *Int. J. Electrochem. Sci.*, 7 (2012) 5977.

- 27. A. R. Bari, M. D. Shinde, V. Deo, L. A. Patil, Indian J. Pure Appl. Phys., 47 (2009) 24.

- 28. R. N. Gayen, K. Sarkar, S. Hussain, R. Bhar, A. K. Pal, Indian J. Pure Appl. Phys., 49 (2011) 470.

- 29. S.J. Pearton, D.P. Norton, K. Ip, Y.W. Heo, T. Steiner, Prog. Mater. Sci., 50 (2005) 293.

- C. Y. Lee, M. Y. Lin, W. H. Wu, J. Y. Wang, Y. Chou, W. F. Su, Y. F. Chen, C. F. Lin, Semicond. Sci. Technol., 25 (2010) 105008.

- 31. H. C. You, Int. J. Electrochem. Sci., 8 (2013) 9773.

- 32. S. Jeong, Y. Jeong, J. Moon, J. Phys. Chem. C, 112 (2008) 11082.

- 33. M. G. Kim, H. S. Kim, Y. G. Ha, J. He, M. G. Kanatzidis A. Facchetti, T. J. Marks, *J. Am. Chem. Soc.*, 132 (2010) 10352.

- K. Vanheusden, C. H. Seager, W. L. Warren, D. R. Tallant, J. A. Voigt, *Appl. Phys. Lett.*, 68 (1996) 403.

© 2016 The Authors. Published by ESG (<u>www.electrochemsci.org</u>). This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).