# Investigation of the Sol-Gel Method on the Flexible ZnO Device

Hsin-Chiang You<sup>1,\*</sup> and Yu-Hsien Lin<sup>2</sup>

<sup>1</sup>Department of Electronic Engineering, National Chin-Yi University of Technology, Taichung, Taiwan <sup>2</sup>Department of Electronic Engineering, National United University, Miaoli, Taiwan \*E-mail: <u>hcyou@ncut.edu.tw</u>

Received: 5 July 2012 / Accepted: 28 July 2012 / Published: 1 October 2012

This paper proposes a sol-gel deposition method applied to ZnO thin film as a semiconductor layer for transistors (TFT). First, various annealing temperatures were applied onto zinc oxide (ZnO) TFT with a bottom gate structure to examine the transistor's characteristics. In annealing at 300 °C, the oxygen vacancies of ZnO thin films demonstrated that the transistor showed the property with an on/off current ratio of up to  $10^5$  and a µsat of 0.06 cm<sup>2</sup>/V-s. Finally, the silicon wafer was substituted by a polyimide substrate, and the sol-gel method in the low-temperature (300 °C) process was developed to fabricate flexible ZnO transistors. The flexible ZnO transistors exhibited a high on/off current ratio (Ion/off) up to  $10^7$  and a µsat of 0.98 cm<sup>2</sup>/V-s.

Keywords: Flexible ZnO Device, Low-Temperature Process, Sol-Gel Method

## **1. INTRODUCTION**

Studies in novel flexible electronics for developing lightweight, low cost, portable, and shockresistant devices such as displays, solar cells, sensors, and radio frequency identification (RFID) mechanisms have increased considerably [1, 2]. However, a-Si:H and polysilicon, which have been commonly used as channel layers for transistors, have several limitations including high temperatures, photosensitivity, and high cost because of their conventional CMOS processes. In flexible electronics, organic semiconductor thin-film transistors have been researched substantially [3]. Organic transistors can be fabricated by processing at near room temperature, and furthermore, can be compatible with flexible plastic substrates. Despite successful demonstrations with flexible organic TFTs, however, they are generally sensitive to operating conditions, and are also unstable under long-term operation [4]. Generally, metal oxide thin films used as electrodes in flat panel displays include  $In_2O_3$ ,  $SnO_2$ , and ZnO. Indium is currently the most commonly used material, but is toxic it is not as cost-effective as zinc. In recent years, ZnO thin films have been considered good candidates for use as metal oxide materials because of their high visible transmittance, conductivity, and low-cost fabrication [5].

Formations of ZnO TFT can be achieved using many methods, including pulsed laser deposition (PLD), metalorganic chemical vapor deposition (MOCVD), and molecular beam epitaxy (MBE). However, these methods are incompatible with flexible electronics manufacturing because either a high-vacuum system or a high-process temperature is required to obtain good electric properties [6].

Currently, most ZnO thin films are deposited by using chemical vapor deposition (CVD) and physical vapor deposition (PVD) methods. CVD and PVD often require a high-vacuum and high-temperature environment, and thus, do not work for flexible electronic roll-to-roll processes integrated for ZnO thin-film deposition. In contrast, the sol-gel method of channel layers offers advantages in enabling the fabrication of a flexible transistor including low cost, low temperature, easy control of deposition parameters, compatibility with large area depositions, and an ability to operate at atmospheric pressure [7, 8, 9, 10, 11].

This paper uses ZnO thin film applied in the channel layer of the transistor to replace OTFT, and the inexpensive and simple solution to deposit the thin film of a channel layer by spin coating. The ZnO TFTs were annealed at low temperature, controlled at approximately 300 °C, and subsequently, polyimide was used to replace the silicon substrate to complete the flexible ZnO TFT.

### 2. EXPERIMENTAL DETAILS

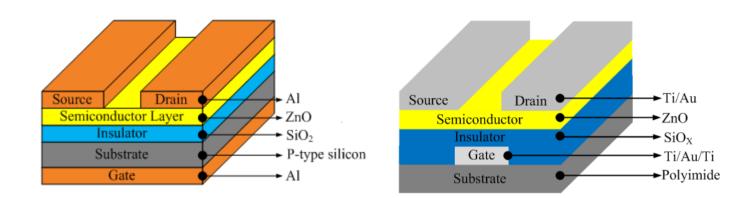

This study examines the electrical performance of ZnO-based TFTs on various substrates at 300 °C (Fig. 1) with a device structure channel width (W) and length (L) of 2000  $\mu$ m and 70  $\mu$ m, respectively. The ZnO precursor solutions were synthesized using zinc acetate dehydrate. These solutions, 0.05M in metal precursors, were prepared in ethanol. These metal oxide solutions were stirred for 30 min at 80 °C before spin coating.

1) Silicon: First, a p-type silicon wafer was treated using RCA clean, and then thermal oxidation was used to grow a SiO<sub>2</sub> film with a thickness of approximately 100 nm. After SiO<sub>2</sub> formation, the surface was treated by oxygen plasma for 30 s.  $ZrO_2$  films were deposited by spin coating at 1000 rpm for 30 s under an ambient temperature of 25 °C. After spinning the ZnO solution, the film was annealed at 300 °C for 1 h in air. Finally, by a thermal evaporation (pressure 10<sup>-6</sup> Torr) process, the wafer back-plated with Al = 300 nm was defined as the gate electrode; a shadow mask was used to define the source and drain, both plated with Al = 300 nm.

2) Polyimide: All the prepared polyimide was treated with ultra sonication in acetone before deposition of the gate electrode to ensure a clean surface. For preparation of a ZnO-based TFT, a Ti/Au/Ti (7 nm/20 nm/7 nm) film was deposited on the polyimide substrate as a gate electrode. A 250-nm-thick SiO<sub>x</sub> layer was grown by plasma-enhanced chemical vapor deposition for the gate insulator. After SiO<sub>x</sub> was treated with O<sub>2</sub> plasma to break the chains on its surface, polar and hydrophilic

functional groups such as OH were introduced on the surface, resulting in an increase of surface energy [6]. Because of the increased surface energy of the SiO<sub>x</sub> insulation, the coverage of the ZnO thin films on the SiO<sub>x</sub> surface was improved. The ZnO precursor solution was spin-coated at 1000 rpm for 30 s onto the SiO<sub>x</sub>. The thin films were then annealed at 300 °C for 1 h in air under standard atmospheric pressure. To fabricate the TFT with contact electrodes, a Ti/Au drain and source electrodes with a thickness of 7 nm/20 nm were deposited by vacuum evaporation (pressure of approximately  $10^{-6}$  Torr) through a shadow mask. An electrical measurement of the ZnO devices was performed with an Agilent 4156 probe station.

(a)

**(b)**

(c)

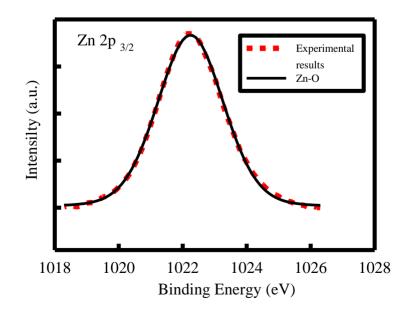

**Figure 1.** A schematic cross-sectional view of the ZnO structure. (b) Schematic bottom gate structure of a flexible ZnO TFT. (c) Photograph of the flexible ZnO TFT.

## **3. RESULTS AND DISCUSSION**

**(a)**

**(b)**

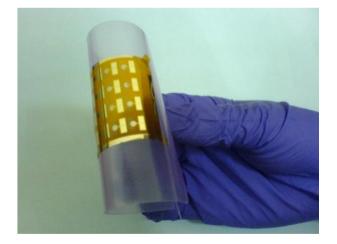

Fig. 2(a) shows the cross-sectional TEM images of the ZnO/SiO<sub>2</sub> structures annealed at 300 °C. The TEM images show that the sol-gel method deposited a smooth semiconductor ZnO film of approximately 4.0 nm in thickness. The surface morphology of the thin film is important in the transistor. Fig. 2(b) shows the AFM images of the sol-gel-derived ZnO thin films. The root mean square (RMS) roughness of the ZnO thin films was 0.635 nm. For the ZnO thin film annealed at 300 °C, the thin-film surface created by the sol-gel method is still smooth. An electron spectroscopy for chemical analysis (ESCA) of ZnO thin films was performed to investigate the chemical bonding states and the impurity content of the constituent elements at 300 °C.

**Figure 2.** (a) Cross-sectional TEM images of sol-gel-derived ZnO/SiO<sub>2</sub> structures annealed at 300°C. (b) AFM images of the ZnO thin films annealed at 300°C, the scanning area of 1  $\mu$ m<sup>2</sup>

0.75

0.50

0.25

0

1.00

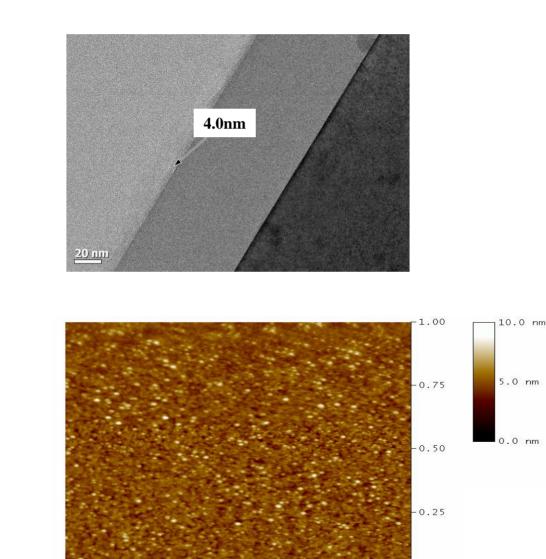

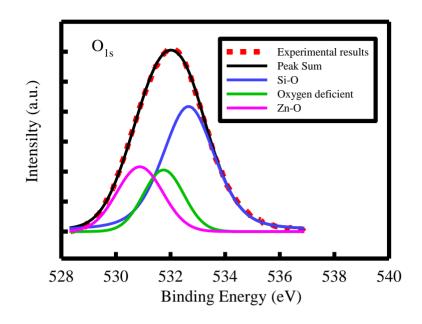

Fig. 3(a) shows the Zn2p<sub>3/2</sub> spectra of the ZnO thin films annealed at 300 °C. The binding energy of Zn2p<sub>3/2</sub> from the hexagonal wurtzite ZnO phase was reported at 1022.4 eV [12, 13]. The data in this study were fitted by a Gaussian curve with peaks centered at 1022.25. Fig. 3(b) shows the O<sub>1s</sub> spectra of the ZnO thin films annealed at different temperatures. The ZnO film's O<sub>1s</sub> ESCA peak in Fig. 3 can be deconvoluted into a spectra of the three peaks located at 532.9 eV, 531.7 eV, and 530.9 eV. The 532.9 eV peak is assigned to hydroxide, the 531.7 eV peak to oxide lattices with oxygen vacancies (oxygen-deficient), and the 530.9 eV peak to oxide lattices without oxygen vacancies (ZnO). The O<sub>1s</sub> peak-fitted binding energy peaks are similar to the results of Lim et al. and Kim et al. [14, 15]. Table 1 shows the performance of the ZnO-based TFT and the flexible ZnO TFT. The threshold voltage (Vth) was extracted from (IDS)<sub>1/2</sub> versus a VGS plot. The saturation mobility (µsat) was calculated from the following equation:

$$I_{DS} = \frac{\mu_{sat} C_i W}{2L} (V_{GS} - V_{th})^2 \qquad V_{DS} > V_{GS} - V_{th}$$

where Ci, W, L, VGS, and Vth are the capacitance of the gate dielectrics per unit area, the channel width, the channel length, the gate bias, and the threshold voltage, respectively.

**Table 1.** Electrical parameters of ZnO-based TFT and flexible ZnO TFT treated with annealingat 300 °C.

|              | $\mathbf{I}_{\mathrm{ON}}\left(\mathbf{A} ight)$ | $\mathbf{I}_{\mathrm{OFF}}\left(\mathbf{A} ight)$ | I <sub>on/off</sub> | $V_{TH}(V)$ | $M_{FE}$ (CM <sup>2</sup> /V-S) |

|--------------|--------------------------------------------------|---------------------------------------------------|---------------------|-------------|---------------------------------|

| ZNO          | 3.81×10 <sup>-6</sup>                            | 2.18×10 <sup>-11</sup>                            | 10 <sup>5</sup>     | 15.6        | 0.06                            |

| FLEXIBLE ZNO | 1.15×10 <sup>-4</sup>                            | 9.25×10 <sup>-11</sup>                            | 107                 | 12.3        | 0.98                            |

**(a)**

**(b)**

**Figure 3.**(a) ESCA spectra for the Zn  $2p_{3/2}$  signals of ZnO thin film annealed at 300°C. (b) ESCA spectra for the O<sub>1s</sub> signals of ZnO thin film annealed at 300°C.

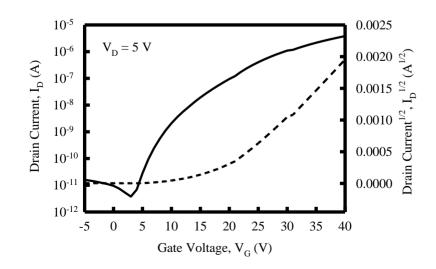

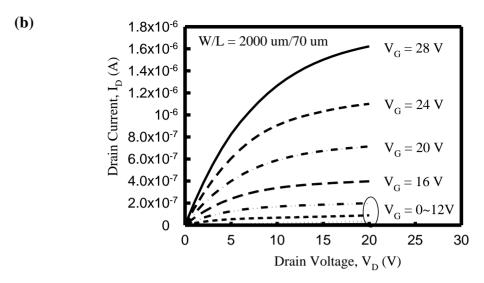

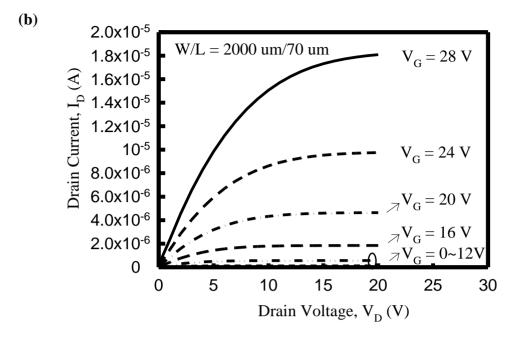

Fig. 4(a) shows the drain current-gate voltage (ID-VG) transfer characteristic curves of ZnO TFT annealed at 300 °C with channel lengths of 70 um and widths of 2000  $\mu$ m. The ZnO TFT exhibited an on-off current ratio (Ion/off) up to nearly 10<sup>5</sup>. The on current (Ion) is able to sustain levels as high as  $3.81 \times 10^{-6}$  A for VD = 5 V, and the off current (Ioff) is low at  $1.59 \times 10^{-11}$  A,  $\mu$ sat of 0.06 cm<sup>2</sup>/V-s and a threshold voltage (Vth) of 15.6 V. Fig. 4(b) displays drain current-drain voltage (ID-VD) output characteristic curves of the ZnO channel annealed at 300 °C; the figure shows an n-type TFT behavior operating in the enhancement mode. This study demonstrates flexible ZnO TFT operation for a device fabricated at a low temperature of 300 °C, as well as on polyimide substrates.

**(a)**

Figure 4. (a)Transfer characteristics curves of ZnO TFT annealed at 300°C by sol-gel method, VD = 5

V. (b) Output characteristics curves of ZnO TFT annealed at 300°C by sol-gel method, VG = 0 to 28 V (step 4 V).

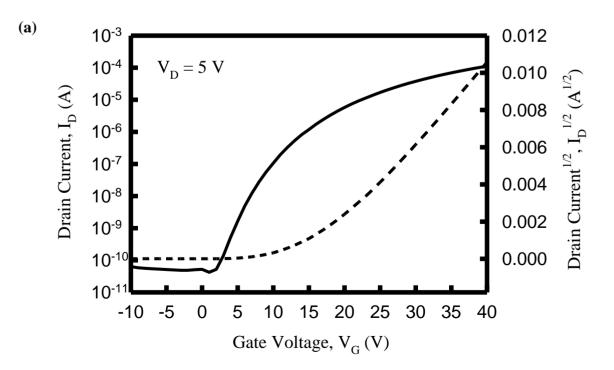

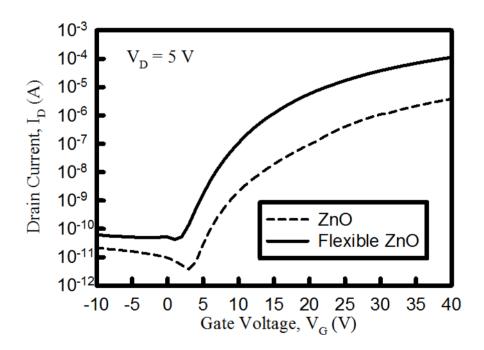

Fig. 5(a) shows the transfer characteristics curves of a flexible ZnO TFT with a channel length of 70  $\mu$ m and a channel width of 2000  $\mu$ m on polyimide, which has a high on current (Ion) of 1.15  $\times$  10<sup>-4</sup> A and an off current (Ioff) of 9.25  $\times$  10<sup>-11</sup> for VD = 5 V. The flexible ZnO TFT exhibited an on-off current ratio (Ion/off) of up to nearly 10<sup>7</sup>. The threshold voltage (Vth) was 12.3 V, and the  $\mu$ sat was 0.98 cm<sup>2</sup>/V-s. Fig. 5(b) shows the drain current-drain voltage (ID-VD) output characteristics curves of the ZnO channel annealed at 300 °C, demonstrating an n-type flexible ZnO TFT behavior operating in the enhancement mode.

Figure 5. (a)Transfer characteristics curves of flexible ZnO TFT annealed at 300°C by sol-gel method, VD = 5 V. (b) Output characteristics curves of flexible ZnO TFT annealed at 300°C by sol-gel method, VG = 0 to 28 V (step 4 V).

**Figure 6.** Transfer characteristics curves of both flexible ZnO TFT and ZnO TFT annealed at  $300^{\circ}$ C by sol-gel method, VD = 5 V.

Fig. 6 shows the transfer characteristics for ZnO on the different polyimide substrates and silicon. The flexible ZnO TFT mobility increases dramatically because of introduced stress; therefore,

the TFT's on-currents on the polyimide substrates were better compared with the transistor manufactured on the silicon substrates [13].

## 4. CONCLUSIONS

This study demonstrates a simple method of fabricating ZnO TFT and flexible ZnO TFT by the sol-gel method and annealing at low temperatures (300 °C). The sol-gel method growth of the semiconductor layer does not require a vacuum system. Experimental results indicate that ZnO TFT and flexible ZnO TFT are better or at least comparable to a conventional transistor, and the flexible ZnO TFT exhibits superior electrical performance. The flexible ZnO TFT exhibited an on-off current ratio (Ion/off) up to nearly  $10^7$ , and the µsat was 0.98 cm<sup>2</sup>/V-s.

#### ACKNOWLEDGMENTS

This work was supported by the National Science Council, Taiwan, under Contract No. NSC 100-2221-E-167-002.

#### References

- H. E. A. Huitema, G. H. Gelinck, J. B. P. H. van der Putten, K. E. Kuijk, C. M. Hart, E. Cantatore, P. T. Herwig, A. J. J. M. van Breemen and D. M. de Leeuw, *Nature* 414 (2001) 599.

- R. H. Reuss, B. Chalamala, A. Moussessian, M. G. Kane, A. Kumar, D. C. Zhang, J. A. Rogers, M. Hatalis, D. Temple, G. Moddel, B. J. Eliasson, M. J. Estes, J. Kunze, E. S. Handy, E. S. Harmon, D. B. Salzman, J. M. Woodall, M. A. Alam, J. Y. Murthy, S. C. Jacobsen, M. Olivier, D. Markus, P. M. Campbell and E. Snow, *Proceedings of the IEEE* 93 (2005) 1239.

- 3. J. Jang, J. W. Kim, N. Park and J.-J. Kim, Organic Electronics 9 (2008) 481.

- 4. K. Song, J. Noh, T. Jun, Y. Jung, H.-Y. Kang and J. Moon, Advanced Materials 22 (2010) 4308.

- 5. K. H. Cho, M. G. Kang, S.-M. Oh, C.-Y. Kang, Y. P. Lee and S.-J. Yoon, *Thin Solid Films* 518 (2010) 6277.

- C. Y. Lee, M. Y. Lin, W. H. Wu, J. Y. Wang, Y. Chou, W. F. Su, Y. F. Chen and C. F. Lin, Semicond. Sci. Technol. 25 (2010) 105008.

- 7. L. Znaidi, Materials Science and Engineering B 174 (2010) 18.

- 8. Y. Natsumea and H. Sakata, Thin Solid Films 372 (2000) 30.

- 9. M. C. Chu, H. C. You, J. S. Meena, S. H. Shieh, C. Y. Shao, F. C. Chang and F. K. Ko, *Int. J. Electrochem. Sci.*, 7 (2012) 5977.

- 10. M. A. Ameer, A. A. Ghoneim and A. M. Fekry, Int. J. Electrochem. Sci., 7 (2012) 4418.

- B. Bermúdez-Reyes, R. Puente-Ornelas, U. M. García-Pérez, P. Zambrano- Robledo, M. E. Contreras-García, J. Morales-Hernández and F. J. Espinoza-Beltrán, *Int. J. Electrochem. Sci.*, 7 (2012) 2028.

- 12. H. Bong, W. H. Lee, D. Y. Lee, B. J. Kim, J. H. Cho and K. Cho, *Applied Physics Letters* 96 (2010) 192115.

- 13. M. N. Islam, T. B. Ghosh, K. L. Chopra and H. N. Acharya, Thin Solid Films 280 (1996) 20.

- 14. M.-G. Kim, H. S. Kim, Y.-G. Ha, J. He, M. G. Kanatzidis, A. Facchetti and T. J. Marks, *J. Am. Chem. Soc.* 132 (2010) 10352.

- 15. S. J. Lim, S. Kwon and H. Kim, Thin Solid Films 516 (2008) 1523.

16. B. Jalan, S. J. Allen, G. E. Beltz, P. Moetakef and S. Stemmer, *Applied Physics Letters* 98 (2011) 132102.

© 2012 by ESG (www.electrochemsci.org)